La memoria es un dispositivo electrónico encargado de almacenar información,

normalmente de forma temporal, aunque también puede ser de forma

permanente. A diferencia de los discos duros u otro sistema de

almacenamiento, el soporte físico está compuesto, como cualquier otro chip, de

silicio, no habiendo partes mecánicas ni móviles.

3.1 Características.

Las memorias, como todos los elementos electrónicos, tienen unos parámetros

o características que diferencian a unas de otras y que, de algún modo,

determinan su utilización y también su calidad. Algunas de estas características

más relevantes de las memorias son las siguientes:

• Volatilidad de la información almacenada. Se dice que una memoria

es volátil, si la información que tiene almacenada desaparece cuando

se elimina la alimentación. En caso contrario, se denomina no volátil.

• Tipo de acceso a los datos. El acceso a un dato concreto que se

encuentra almacenado en la memoria puede ser llevado a cabo de dos

formas distintas: secuencial o aleatoria. En el acceso secuencial, para

leer o escribir un dato en la posición de memoria n, deberemos haber

accedido previamente a todos los datos anteriores; en el caso de

memoria de acceso aleatorio, podremos acceder a cualquier posición de

memoria de forma independiente, sin tener en cuenta las posiciones

anteriores, son las que más se usan.

La memoria se estructura como una matriz bidimensional formada por

filas y columnas, por lo que un dato concreto en la memoria se identifica

por una coordenada formada por la fila y columna donde se encuentra

en dicha matriz. No obstante, cuando se direccionan los datos en la

matriz primero se seleccionan las columnas y, posteriormente, se busca

el dato o los datos deseados direccionando las filas correspondientes

hablándose, por tanto, de dos ciclos de acceso:

Ciclo de acceso CAS (Column Access Strobe): Acceso a la

columna donde se encuentra el dato o los datos.

Ciclo de acceso RAS (Row Access Strobe): Selección de la fila

donde se encuentra el dato en la columna seleccionada en el

acceso CAS.

La selección de un dato requiere al menos de un ciclo CAS y un ciclo

RAS. Si son varios datos de una misma columna los requeridos, lo

normal es que la memoria requiera un ciclo CAS y varios RAS.

• Dinámicas o Estáticas. Las memorias dinámicas necesitan que la

información almacenada sea refrescada cada cierto tiempo. Debido a

que las celdas de memoria se estructuran en filas y columnas, el

refresco de la memoria no se realiza celda por celda, sino fila por fila o

columna por columna, según sea su acceso, lo que agiliza en gran

medida esta operación. El refresco consiste en regrabar todas las celdas

de memoria cuya información es un “1” lógico en el momento del

refresco y suele hacerse en los ciclos o estados en los que la memoria

está inactiva, aunque también se aprovechan los ciclos de lectura o

escritura para realizar el refresco de toda la fila en la que se encuentra el

dato que se desea modificar o leer. El refresco debe ser constante y la

cadencia de refresco del orden de milisegundos, lo que nos puede hacer

pensar que estas memorias deben ser lentas; Sin embargo, las

memorias dinámicas son muy rápidas y baratas, puesto que cada célula

de información lo compone un condensador construido con transistores

o células CMOS. Las memorias Estáticas no tienen el inconveniente del

refresco, sin embargo, su estructura interna es bastante más compleja y

eso hace que sean más caras que las anteriores y que el nivel de

integración sea inferior. En general, estas memorias son mas rápidas

que las anteriores, como ejemplo podemos citar las memorias utilizadas

como caché, que alcanzan tiempos de acceso inferiores a los 10 ns,

aunque son de mucha menos capacidad que las dinámicas, del orden de

250 KB hasta 1 MB.

• Velocidad, Frecuencia y Tiempo de acceso. La velocidad de una

memoria se da, normalmente, por su frecuencia o por su periodo, que es

la inversa de la frecuencia, de forma que, una memoria de 100 MHz

también se puede denominar, en cuanto a velocidad, de 10ns ya que

1/100 MHz = 10 ns. Sin embargo, ni la frecuencia ni su periodo nos dan

una idea real de la velocidad de la misma, ya que lo importante sería el

tiempo que tarda un dato en leerse de la memoria o en escribirse en la

misma, según sea el caso. Este tiempo se denomina tiempo de acceso

y, se expresa en nanosegundos (ns) y depende de muchos factores

entre los que podemos destacar la latencia o retardo al direccionar la fila

y columna en las que se encuentra el dato o datos requeridos:

o Latencia CAS (Column Access Strobe). Es un parámetro que nos

indica la demora que se produce desde que se da la orden de

selección hasta que la columna está direccionada.

o Latencia RAS (Row Access Strobe). Es un parámetro que nos

indica la demora que se produce desde que se da la orden de

selección hasta que la fila está direccionada y el dato preparado.

La latencia RAS es muy inferior a la latencia CAS, por lo que en la

referencia de los integrados de memoria sólo se suele indicar el valor de

esta última referida a los tiempos de reloj que dura. Por ejemplo, una

latencia CAS de 3 implica que dura 3 ciclos de reloj. Los valores típicos

en las memorias actuales suelen ser 2 y 3, aunque también se pueden

encontrar memorias con otros valores mayores como 4 o 5.

• Ancho de banda o velocidad de la memoria. Este parámetro puede

entenderse como la velocidad a la que la memoria puede aceptar datos

(escritura) o puede entregar datos (lectura) de forma continua, aunque

debemos tener en cuenta que la memoria no está continuamente

recibiendo o entregándolos, sino que lo hace en ráfagas más o menos

largas. Si la memoria es de 8 bits, el ancho de banda se puede dar tanto

en MHz (no confundir este dato con la frecuencia de la memoria) como

en MBytes/segundo, ya que estos valores coincide y se calculan como la

inversa del tiempo de acceso de la memoria, por tanto, una memoria

con un tiempo de acceso de 10 ns y un bus de datos de 8bits tiene un

ancho de banda teórico de 100 MHz o 100MB/s, ya que 1/10-8 s = 108

Hz = 100 MHz 100MHz x 1Byte = 100 MB/s. Las memorias actuales

utilizan un bus de datos de 64 bits e incluso de 128 bits, por lo que el

ancho de banda se da únicamente en MB/s o en GB/s no coincidiendo

este valor con la frecuencia de funcionamiento de la memoria. Por

ejemplo, una memoria con un tiempo de acceso de 10 ns y 64 bits de

datos tendrá un ancho de banda máximo de 100MHz x 8 bytes = 800

MB/s.

• Memorias Síncronas y Asíncronas. Las memorias asíncronas no

utilizan ningún reloj para que el dato sea leído o escrito en su interior,

simplemente necesita que una serie de terminales sean activados para

que el dato se lea o se escriba; Sin embargo, actualmente se emplean

memorias síncronas (como las SDRAM) que requieren de un reloj que

marque las pautas de lectura o escritura de los datos. Estas memorias

se denominan síncronas y trabajan normalmente a la velocidad del bus

del sistema SFB. Este modo de trabajo permite que las memorias

alcancen mayor velocidad manteniendo otras características, como ser

dinámicas y necesitar refresco.

• Modo burst (ráfaga). Las memorias que implementan el modo burst

están preparadas para realizar operaciones de lectura o escritura de

bloques de memorias contiguos de forma muy rápida. En general,

cuando el micro quiere leer o escribir en una zona completa de memoria

que ocupa varias posiciones consecutivas, debe ir indicando a la

memoria, una por una, a qué dirección quiere acceder y posteriormente

leer o escribir el dato. En las memorias que admiten el modo burst, el

micro sólo debe indicar cual es la primera dirección de memoria y la

longitud del bloque que desea leer o escribir; posteriormente, en

operaciones de escritura, el micro sólo envía datos y es la memoria

quien va incrementando su contador de direcciones para que cada dato

que entra se sitúe uno a continuación del anterior. En las operaciones de

lectura, una vez que se indica la posición del primer dato y el número de

datos que deseamos leer, el micro sólo tiene que ir leyendo todos los

datos que la memoria le va depositando en el bus de datos sin tener que

ir indicando en que posición se encuentra cada uno de ellos. La

velocidad se incrementa considerablemente, sobre todo en las memorias

síncronas, en las cuales este modo de trabajo es el ideal.

• Modo Pipeline. Esta característica suele implementarse sólo en las

memorias estáticas que se utilizan como caché del microprocesador. En

general, las memorias deben terminar un ciclo de lectura o escritura para

poder comenzar el siguiente, pues bien, las memorias que admiten el

modo pipeline pueden ir preparando el siguiente o siguientes datos

antes de que el que está en proceso haya concluido, es similar al modo

pipeline utilizado en el registro de instrucciones del microprocesador.

Las actuales cachés L1 suelen incorporar este modo de funcionamiento,

tanto en la porción destinada a las instrucciones, como la destinada a los

datos, incrementándose el rendimiento de la misma.

• Paridad (parity). No es una característica de un tipo de memoria, sino

de un módulo compuesto por distintos chips de memoria. Los módulos

de memoria que no implementan la paridad trabajan directamente con

datos de 8, 16 o 32 bits y, por tanto, no se realiza ningún control del flujo

de datos. Los módulos que implementan la paridad utilizan un bit más

para forzar la paridad de los datos que entran o salen del módulo. La

paridad puede ser par o impar:

o Paridad PAR: El número de “1” en cada dato es un número par,

por ejemplo: 010111000 o 111011001. El bit de más a la

izquierda (mayor peso) se denomina bit de paridad. Para que un

tren de datos contenga paridad par, sólo tendremos que

incorporar el bit de paridad adecuado, de forma que a los datos

pares se le añadirá como bit de paridad un “0” para no modificarlo

y los datos que tengan paridad impar se le añadirá como bit de

paridad un “1”, de forma que la paridad resultante será par.

o Paridad IMPAR: El número de “1” en cada dato es un número

impar, por ejemplo: 110111000 o 011011111.

Si un dato (con bit de paridad) con paridad par llega a una memoria

configurada para que todos los datos que reciba sean impares, detectará

un error, pero no podrá corregirlo. Igualmente pasará si un dato impar

llega a una memoria preparada para recibir datos con paridad par.

Como conclusión, podemos decir que las memorias sin paridad no

detectan fallos en el flujo de datos y las memorias con paridad sí pueden

detectar el cambio de un bit en el flujo de datos, pero no puede saber

donde se encuentra el error.

• Códigos de detección y corrección de errores ECC: Los códigos

ECC (Error Correction Code) no sólo permiten detectar si se producen

errores en el flujo de datos de una memoria, sino que también permiten

corregirlos sin que el sistema se detenga. Por tanto, los sistemas que

incorporan memorias ECC son mucho más estables, lo que les hace

muy atractivos para ser utilizados en los servidores para redes LAN y

WAN.

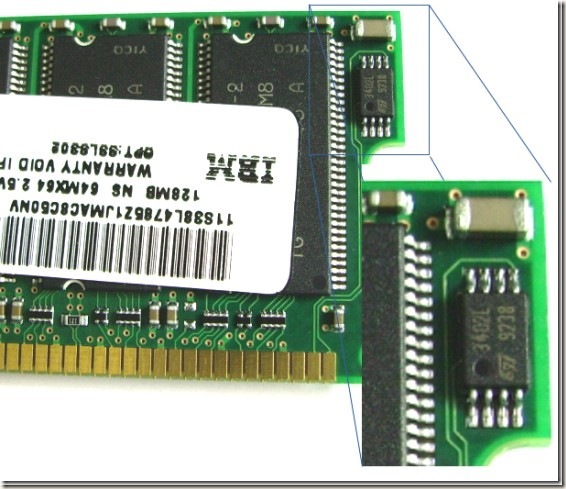

• SPD – Serial Presence Detect. Permite a la BIOS de la placa madre

identificar las características de los módulos de memoria y, de esta

forma, configurar los parámetros de la memoria para un funcionamiento

óptimo. Consiste en un pequeño integrado de memoria EEPROM serie

que se añade al módulo de memoria con la información de las

características del módulo en cuestión. En la actualidad lo implementan

muchos fabricantes en sus memorias SDRAM, DDR y DDR2 SDRAM y

RDRAM.

Ilustración 3.1. Vista de la memoria EEPROM serie del sistema SPD.

3.2 Tipos

Vistas todas las características de las memorias es fácil comprender que habrá

muchos tipos distintos de memoria según utilicen unas u otras de estas

características. A continuación se comentan los tipos de memorias utilizados en

la actualidad, o que aun pueden encontrarse en equipos en servicio.

3.2.1 ROM.

Las memorias ROM (Read Only Memory) o memorias de sólo lectura se

caracterizan precisamente por que su contenido se graba en fábrica durante el

proceso de fabricación y el usuario sólo puede leerla. Su principal característica

es que son memorias no volátiles y, por tanto, la información grabada en

fábrica permanece invariable durante toda la vida útil de la memoria. Son

utilizadas para implementar el firmware del sistema o la BIOS de inicialización y

configuración del sistema. Otra característica de este tipo de memoria es su

bajo nivel de integración, lo que implica capacidades bajas de memoria. Las

utilizadas en los PC suelen ser de 32 Kb o 64 Kb, aunque algunos modelos

utilizan capacidades mayores.

3.2.2 PROM.

Las memorias PROM (Programed ROM), o ROM programables eléctricamente,

son similares a las anteriores excepto en la grabación, que no se realiza en el

proceso de fabricación, sino que se realiza con unos aparatos denominados

grabadores de PROMs. Sólo pueden grabarse una única vez y son no

volátiles. También mantienen un muy bajo nivel de integración y su utilización

se limita a la realización de prototipos o como sistema de configuración de

tarjetas electrónicas, sustituyendo a los puentes.

3.2.3 EPROM.

Las memorias EPROM (Erasable PROM) o

memorias PROM cuyo borrado se realiza

aplicando rayos UVA, con una longitud de

onda determinada por el fabricante, a través

de una ventana que incorpora el circuito

integrado a tal efecto. Por tanto, pueden ser

grabadas y borradas multitud de veces. Al

igual que las memorias ROM son no volátiles y se utilizan en los PC para

almacenar el firmware o BIOS.

Ilustración 3.2. Chip de memoria

EPROM correspondiente a una

BIOS de AWARD.

3.2.4 EEPROM o E2PROM.

Las memorias EEPROM (Electrical EPROM) o E2PROM son similares a las

anteriores pero, en este caso, el borrado se realiza eléctricamente, al igual que

su programación. Actualmente se utilizan versiones de este tipo de memorias

denominadas FLASH que permiten al usuario la actualización de la BIOS del

sistema mediante unos programas diseñados por los fabricantes de placas

madre.

3.2.5 RAM.

Las memorias RAM (Random Access Memory), memorias de acceso aleatorio,

son memorias volátiles y no deben su nombre a ninguna característica que las

diferencie de las anteriores, puesto que también las memorias ROM, PROM,

EPROM y EEPROM permiten el acceso aleatorio a sus datos. Al pertenecer al

grupo de memorias volátiles no puedan ser utilizadas para almacenar el

firmware o BIOS del sistema. Existe una gran variedad de memorias que

pueden englobarse con este nombre y que iremos definiendo a continuación de

acuerdo a sus características principales.

3.2.6 DRAM.

Las memorias DRAM (Dynamic RAM), como su nombre indica son memorias

RAM dinámicas, es decir, necesitan refrescar sus datos para que estos

permanezcan almacenados. Está estructurada como una matriz de “n” filas por

“m” columnas, de forma que, cualquier dirección que se le envíe debe

descomponerse en un par de coordenadas correspondientes a la fila y columna

donde se encuentra el dato. Cada acceso a la memoria, ya sea en lectura o

escritura, implica una decodificación de la fila y la columna correspondiente.

Estas coordenadas se aplicarán a la matriz y posteriormente se validarán, en

este momento la matriz nos entregará el dato a leer o escribirá en la posición

seleccionada el dato que le proporcionemos en el bus de datos.

Es importante tener en cuenta que en los equipos actuales, el

microprocesador no lee directamente de la memoria RAM, sino de la memoria

caché y, por tanto, es ésta quien se comunica directamente con la RAM. Si

tenemos en cuenta que las memorias caché están diseñadas para trabajar, no

con datos, sino con ráfagas de datos, es lógico pensar, que también las

memorias RAM se diseñen en ese sentido. Cada vez que se lee un dato de una

fila concreta, todos los datos de dicha fila son refrescados. También se realiza

un refresco secuencial durante los tiempos de inactividad de la memoria, de

este modo, se impide la pérdida de datos si el micro no está utilizando una

cierta zona de la memoria.

Son las utilizadas en los PC como memoria RAM y podemos encontrar

distintos tipos que han ido evolucionando poco a poco.

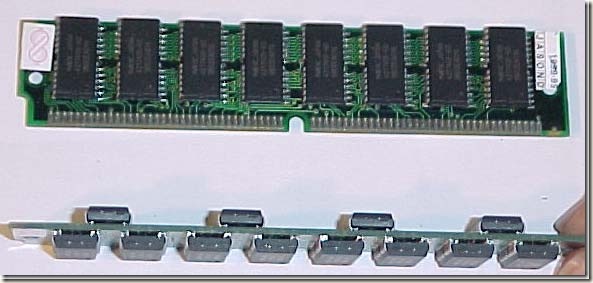

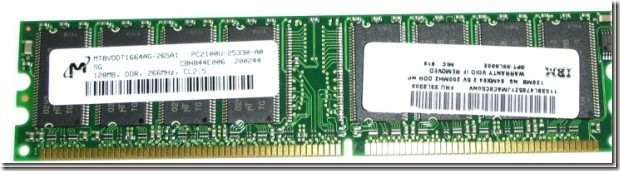

3.2.6.1 FPM RAM.

Puede decirse que fueron las primeras memorias utilizadas en forma de

módulos se componían de varios chips, como puede observarse en la

ilustración. Fue utilizado en la mayoría de equipos con procesadores 386 y 486

y también la utilizaron los primeros Pentium que aparecieron en 1994. Este tipo

de memorias se presentaba en módulos SIMM (Single In-line Memory Modulo)

de 30 contactos, utilizando un bus de datos de 8 bits. Esto implicaba que un

banco de memoria debía estar compuesto por cuatro módulos para completar

el bus de 32 bits del sistema utilizado en los 386 y 486. También se encuentra

en módulos de 72 contactos (32 bits) para las últimas placas 486 y las placas

para Pentium. En este caso, los bancos de memoria constaban de un único

módulo en los sistemas 486 con bus de datos de 32 bits y de dos módulos para

completar la longitud del bus externo de datos del Pentium que es de 64 bits.

También se usó en las tarjetas gráficas, aunque existe un tipo con doble

puerto, llamada VRAM, más específico para este tipo de tarjetas y que veremos

más adelante.

Su nombre viene de las

siglas correspondientes a Fast

Page Mode RAM (RAM con

modo de paginación rápida), ya

que incorporan un sistema de

paginación que incrementa

considerablemente la velocidad

de lectura o escritura al

considerar que el siguiente dato

estará posiblemente en la misma columna o fila que el anteriormente leído o

escrito. La primera vez que se accede a una fila, el controlador de memoria

deberá descomponerla en la fila y columna donde se encuentra el dato, pasar

estos datos a la memoria y validarlos. Si el siguiente dato se encuentra en la

misma fila, no será necesario acceder a la matriz para validar la fila, puesto que

ya está activa y, por tanto, nos ahorraremos ese tiempo en la lectura o escritura

del dato. Con el resto de datos sucederá lo mismo, pero si el dato cambia de

fila, entonces se deberá comenzar el proceso de cálculo de fila y validación en

la matriz. Como consecuencia, si los datos que se desean leer o escribir se

encuentran en una misma fila, la transferencia se agiliza considerablemente,

pero si se encuentran en distintas filas, las memorias FPM se comportan de

forma tradicional.

Normalmente se leen o escriben paquetes de 4 datos denominados

ráfagas (Burst), siendo el número de ciclos de lectura o escritura de cada dato

que forman la ráfaga distintos. El ideal sería una memoria con los cuatro

tiempos iguales a “1”, que se denominaría 1-1-1-1, pero lo normal es que se

produzcan tiempos de espera entre datos y salgan combinaciones del estilo 4-

3-3-2 o similares; esto significa que utiliza 3 ciclos de espera para el primer

dato, 2 ciclos de espera para el segundo y tercer dato y 1 ciclo en el último. En

Ilustración 3.3. Módulos SIMM de memoria FPM

RAM.

el caso de las memorias FPM, la ráfaga más favorable es la 5-3-3-3, es decir,

una ráfaga que utiliza 14 ciclos de reloj para enviar 4 datos, o lo que es lo

mismo, una media de 3,5 ciclos de reloj por dato. Pues bien, si utilizamos un

bus de 66 MHz, tendremos que cada ciclo de reloj es de 1/66 106=15 ns, por

tanto, 3,5 ciclos de reloj tienen una duración de unos 52 ns, lo que implica que

deberemos utilizar memorias rápidas de al menos 50 ns para que el

funcionamiento sea lo más estable posible. En sistemas con buses de 33 MHz,

basta utilizar memorias de 70 ns. En la realidad, se han estado utilizando

memorias de 60 ns en buses de 66 MHz, esto suponía simplemente un

descenso del rendimiento teórico, puesto que las ráfagas se fijaban a valores

superiores al máximo teórico de 5-3-3-3.

3.2.6.2 EDO RAM.

La memorias EDO (Extended Data Output) constituyen una mejora respecto a

las anteriores y tratan de suplir el problema que tenían las FPM durante los

tiempos de espera, es decir, ¿qué hacía el microprocesador durante los

tiempos de espera en la lectura o escritura de un dato?, pues bien, la respuesta

es muy simple, nada. Estas memorias se presentan en módulos SIMM de 72

contactos (32 bits) y en módulos DIMM (Dual In-line Memory Modules) de 168

contactos (64 bits), en este último caso los bancos están constituidos por un

único módulo DIMM.

Las memorias EDO utilizan la

técnica pipeline para agilizar los

procesos de transferencia de datos,

es decir, mientras aun se está

leyendo el último dato ya se está

preparando el siguiente, utilizándose

así los tiempos de espera para algo

más que no hacer nada. Esta mejora

se realiza mediante un nuevo buffer

de salida que almacena el dato al que se acaba de acceder, de este modo, el

sistema puede ir buscando el siguiente dato aunque no se haya leído aun el

anterior. Con esta técnica se mejora el esquema de la ráfaga que puede llegar

a ser 5-2-2-2, bastante mejor que la utilizada por las memorias FPM, aunque

no mejoran el tiempo del primer acceso. Este modo de funcionamiento se

denomina Extended Data Output, de donde reciben estas memorias el

nombre EDO RAM. Su constitución interna es básicamente igual que el de las

memorias FPM con una mínima circuitería adicional.

Ilustración 3.4. Módulos de memoria EDO RAM

3.2.6.3 BEDO.

La memoria BEDO (Burst Extended Data Output) fue diseñada originalmente

para el conjunto de chipsets de Intel 82430HX para soportar mayores

velocidades de BUS. La diferencia fundamental respecto a la anterior es que es

.

capaz de transferir datos a la velocidad del reloj, pero no de forma continua,

sino a ráfagas (burst).

3.2.6.4 SDRAM.

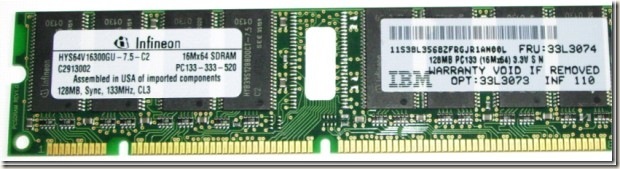

Las memorias SDRAM (Synchronous RAM), o DRAM síncronas, se

comenzaron a utilizar con los Pentium II con arquitectura de bus de 100 MHz,

dada la imposibilidad de las memorias EDO RAM de llegar a trabajar a estas

frecuencias. Se presentan únicamente en módulos DIMM de 168 contactos (64

bits).

Como su nombre indica, esta

memoria debe funcionar de forma

síncrona (a la misma velocidad) con

el bus al que se conecta, por lo que

requieren ser memorias muy rápidas.

Para un bus de 100MHz, las

memorias tienen que ser de 1/100MHz = 10 ns. Por tanto, en las placas que

permiten configurar la velocidad del bus del sistema, podremos hacer trabajar a

la memoria SDRAM a 66, 100 o 133 MHZ, aunque deberemos asegurarnos de

que la SDRAM sea capaz de soportar dicha velocidad.

Actualmente se utilizan varias técnicas para que estas memorias

optimicen el tiempo de acceso a los datos sin tener que modificar la estructura

de la matriz de datos que caracteriza a las memorias DRAM. Estas técnicas

son:

• Latencia CAS (Column Access Strobe) programable: Permite

programar (por medio de la BIOS) esta característica para que se adapte

de la mejor forma posible al sistema en el que se ha implantado la

memoria. Los módulos actuales suelen implementar la función

denominada SPD (Serial Presence Detect, detección de presencia

serie,) que permite a la BIOS detectar automáticamente la latencia CAS

optima y configurarla.

• Sincronización: Permite que sea el reloj del sistema quien controle la

transferencia de datos, simplificando así el número de señales

implicadas en las transferencias, tanto de control como de direcciones,

lo que permite aumentar la frecuencia de trabajo del dispositivo.

• Pipeline: Permite buscar un dato mientras que el anterior se está

procesando.

• Utilización de bancos independientes: Consiste en dividir las matrices

en dos o cuatro, de forma que, mientras se utiliza una se pueda estar

preparando un dato en otra.

Ilustración 3.5. Módulo de memoria SDRAM.

• Burst: En estas memorias se puede programar la longitud de la ráfaga

(burst) mediante un registro que se configura en la BIOS del sistema.

También se puede programar el tipo de ráfaga utilizada entre lineal

(todos los datos de la ráfaga son consecutivos) o interpolado (los datos

pueden estar salteados).

Se han comercializado con los nombres PC66, PC100 y PC133 según

estén diseñadas para un bus de 66 MHz, 100MHz o 133 MHz respectivamente.

La memoria SDRAM, bien sean PC66, PC100 o PC133, tiene un ancho

de bus de datos igual a 64 bits, lo que significa que en cada ciclo de reloj

(cada Hz) envía 64 bits = 8 bytes. De esta forma, su capacidad de transferencia

de datos teórica (es decir, su velocidad útil teórica) será:

PC66: 8 bytes/ciclo x 66 MHz = 533 MB/s

PC100: 8 bytes/ciclo x 100 MHz = 800 MB/s = 0,8 GB/s

PC133: 8 bytes/ciclo x 133 MHz = 1066 MB/s = 1,06 GB/s

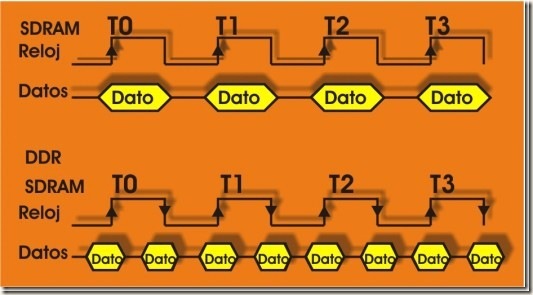

3.2.6.5 DDR y DDR2 SDRAM.

Las memoria DDR SDRAM (Double Data Rate SDRAM) o SDRAM de doble

velocidad de datos permiten la sincronización de la transferencia de datos,

tanto en el flanco de subida del ciclo de reloj del sistema, como en el flanco de

bajada. De esta forma se divide por dos el tiempo de acceso, o lo que es lo

mismo, se multiplica por dos la velocidad de transferencia de datos, de igual

forma se multiplica por dos el ancho de banda teórico.

Ilustración 3.6. Comparativa de los cronogramas de una memoria SDRAM y una memoria DDR

SDRAM.

Se presenta en módulos DIMM con las mismas dimensiones que los de las

memorias SDRAM, pero en este caso con 184 contactos y tiene una única

muesca en lugar de las dos muescas de las SDRAM.

En la denominación de las memorias DDR, en lugar de su frecuencia se

indica su ancho de banda, de forma que una memoria de 200 MHZ y 64 bits,

cuyo ancho de banda es 200 MHz x 2 x 8 Bytes = 3200 MB/s, se denomina

PC3200, en lugar de PC200 como sucedía con las SDRAM. También se

denomina DDR400, aunque esta denominación no es tan corriente como

PC3200.

Ilustración 3.7. Módulo de memoria DDR SDRAM de 512 MB y 400 MHz – PC3200.

Las memorias DDR2 son la evolución lógica de las memorias DDR que ya

se están quedando lentas y obsoletas para las nuevas placas y micros

actuales. Entre las diferencias más destacables de estas memorias respecto a

sus predecesoras DDR podemos citar las siguientes:

Tensión de alimentación: DDR = 2,5 voltios, DDR2 = 1,8 voltios.

Módulo DIMM: DDR = 184 contactos, DDR2 = 240 contactos. No

son compatibles entre sí.

Latencia CAS: DDR = 2, 2,5 y 3 DDR2 = 3, 4 y 5. Este parámetro es

superior en las DDR2 que en las DDR.

Frecuencias de memoria superiores a 600 MHz y anchos de

banda superiores a 5 GB/ s en memorias de canal simple y 10

MB/s en memorias de canal doble.

Pueden trabajar en placas madre con chipset o microprocesadores que

implementen un controlador de memoria de doble canal de datos para la

memoria, esto quiere decir, que puede manejar al tiempo dos bancos distintos

de memoria emparejándolas como si de un banco de doble capacidad y doble

velocidad se tratara, aunque esto último, doble velocidad, no es del todo cierto.

Ilustración 3.8. Módulo de memoria DDR2 SDRAM de 512 MB y 675 MHz – PC5400.

3.2.6.6 RDRAM.

Este tipo de memorias, denominadas también Direct Rambus DRAM,

por ser Rambus el fabricante y principal desarrollador, incorporan buses de

datos muy pequeños para poder alcanzar altísimas velocidades de

transferencia que superan los 533 MHz, con picos de transferencia de 1,6GB/s

en ráfagas de 2 ns.

Ilustración 3.9. Módulos de memoria RDRAM.

La Rambus tiene un bus de datos más estrecho, de sólo 16 bits = 2 bytes, pero

funciona a velocidades mucho mayores, de 300, 356 y 400 MHz. Además, es capaz de

aprovechar cada señal doblemente, de forma que en cada ciclo de reloj envía 4 bytes en

lugar de 2.

Debido a este doble aprovechamiento de la señal, se dice que la Rambus funciona a

600, 712 y 800 MHz “virtuales” o “equivalentes”. Y por motivos comerciales, se la denomina

PC600, PC700 y PC800. Por todo ello, su capacidad de transferencia es:

Rambus PC600: 2 x 2 bytes/ciclo x 300 MHz = 1,2 GB/s

Rambus PC700: 2 x 2 bytes/ciclo x 356 MHz = 1,42 GB/s

Rambus PC800: 2 x 2 bytes/ciclo x 400 MHz = 1,6 GB/s

Como los procesadores actuales tienen un bus externo de datos de 64

bits o 128 bits, deberemos utilizar varios módulos RDRAM para cubrir todas las

líneas de datos, multiplicando así la velocidad de transferencia por el número

de chips implementados; por ejemplo, si utilizamos 4 módulos RDRAM de

400MHZ (1,6GB/s) y 16 bits para cubrir la memoria de un Pentium IV de 64 bits

de bus de datos externo, el ancho de banda máximo efectivo sería de 4 X 1,6

GB/s = 6,4 GB/s equivalente a una memoria DDR SDRAM PC6400.

3.2.7 SRAM.

Las memorias SRAM o RAM estáticas (Statics RAM) tienen tiempos de acceso

muy pequeño, inferior a los 10 ns y no necesitan refresco, sin embargo, su

precio es muy alto en relación con las memorias DRAM. Este tipo de memorias

se utiliza normalmente como memoria Caché del sistema, tanto de nivel 1

como de nivel 2, ya que la memoria caché suele tener un tamaño inferior a 1

MB de memoria.

Al igual que con las memorias DRAM, podremos encontrar memorias

SRAM síncronas, burst o pipeline, que mejoran las características técnicas de

la memoria SRAM básica. Todas estas técnicas son imprescindibles para una

buena memoria caché en los sistemas actuales.

o Asynchronous Static RAM (Async SRAM): La antigua caché de

los 386, 486 y primeros Pentium, más rápida que la DRAM, pero

que provoca igualmente estados de espera en el procesador. Su

velocidad es de 20 ns, 15 ns y 12 ns.

o Synchronous Burst Static RAM (Sync SRAM): Es la mejor para un

bus de 66MHz y puede sincronizar la velocidad de la caché con la

del procesador. Su velocidad es de 8.5 ns a 12 ns.

o Pipelined Burst Static RAM (PB SRAM): Funciona de manera

continuada sincronizada con el procesador a velocidades de

hasta 133 MHz. Tarda un poco más en cargar los datos que la

anterior, pero una vez cargados, el procesador puede acceder a

ellos con más rapidez. Su velocidad es de 4.5 ns a 8 ns.

3.2.8 Tag RAM.

Esta memoria, a diferencia de las DRAM, no almacenan datos, sino

direcciones. Concretamente almacenan las direcciones de los datos, de la

DRAM, que ya están almacenados en la memoria caché. De este modo,

cuando el microprocesador va a buscar un dato, comprueba la dirección en la

Tag RAM, si se encuentra allí, va directamente a la caché a buscarlo y en caso

contrario se dirige a la DRAM.

Cuando se habla de Cacheable Memory en las placas actuales, nos

referimos a la cantidad de memoria principal susceptible de ser cacheada o, lo

que es lo mismo, con posibilidad de ser almacenada en la caché, por tanto, una

placa que contenga un chipset con capacidad de “cachear” 64 MB no verá

incrementado prácticamente su rendimiento si se le incorporan más de estos

64 MB de memoria principal. Esto es lo que sucede con el chipset 430TX, que

no permite utilizar con la caché más de 64 MB, sin embargo el 430 Hx sí lo

permite.

3.2.9 VRAM.

La memoria VRAM o RAM de vídeo es la utilizada por las tarjetas gráficas para

escribir en ellas la información que se visualiza en el monitor. La tarjeta de

vídeo o tarjeta gráfica es un periférico de los denominados memory mapped,

es decir, el procesador escribe en una determinada zona de memoria y la

tarjeta de video lee esos datos en la misma zona de memoria. Por tanto, se

puede producir el caso en el que el procesador y tarjeta de vídeo intenten

acceder a la memoria de vídeo al mismo tiempo. Por este motivo, las memorias

VRAM se diseñan con un doble puerto o doble acceso que permite al

controlador de vídeo y al procesador acceder al mismo tiempo a la memoria.

Ilustración 3.10. Vista de los chips de memoria VRAM en una tarjeta de vídeo.

Esta memoria suele venir incorporada en la controladora de vídeo y en la

mayoría de los casos es ampliable. En las tarjetas de vídeo antiguas, que no

soportaban texturas ni gráficos en 3D, la ampliación suele realizarse mediante

chips de memoria que se insertan en los zócalos que llevan las controladoras,

en las actuales placas, la ampliación se realiza mediante módulos especiales

que se insertan en unas ranuras o slots de la tarjeta controladora.

3.3 Módulos SIMM Y DIMM.

Es el nombre que reciben los circuitos impresos o tarjetas de memoria en

forma de plaquitas alargadas en las que se distribuyen o montan los chips de

memoria. Estas plaquitas disponen de una hilera de conexiones que se acoplan

al ordenador a través de los slots de memoria correspondientes. Se

caracterizan por el número de conexiones, bits que pueden leer o escribir en

una única operación de lectura o escritura y su tensión de funcionamiento.

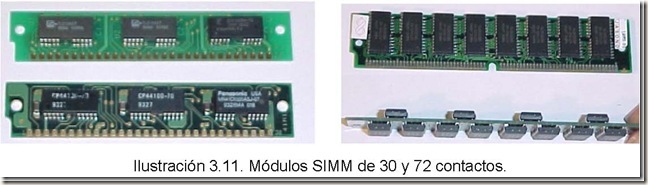

• SIMM: Single In-line Memory Module, son módulos cuyas conexiones

con el zócalo aparecen únicamente en un lado de la placa de circuito

impreso que compone el módulo o, en algunos casos, también se

podrían considerar SIMM los módulos que tienen conexiones a ambos

lados, en los cuales, las conexiones de un lado son una réplica de los

existentes en el otro lado de la placa de circuito impreso para asegurar

así él contacto de los terminales. Aparecieron con las placas madre de

los primeros 80286 y 80386, siendo estos módulos SIMM de 30

contactos y se mantuvieron hasta las placas madre de los Pentium MMX

y K6- 2 de AMD en los módulos SIMM de 72 contactos. Los módulos de

30 contactos miden 8,5 cm y tienen un bus de datos de 8 bits, por lo que

en un 386 o 486 que tiene un bus de datos de 32 bits hay que colocarlos

en grupos de 4 módulos denominados bancos, siendo muy importante

que todos los módulos de un mismo banco sean idénticos. Los SIMMs

de 72 contactos miden 10,5 cm, son algo más modernos, pero tuvieron

una vida corta ya que pronto fueron desplazados por los módulos DIMM.

Tienen un bus de datos de 32 bits, por lo que se usan de 1 en 1 en los

486 y en bancos de 2 módulos iguales en las placas madre para

Pentium MMX y K6- 2 de AMD, ya que su bus de datos es el doble (64

bits). Tanto en un caso como en el otro, los zócalos suelen ser de color

blanco

Ilustración 3.11. Módulos SIMM de 30 y 72 contactos.

• DIMM: Dual In-line Memory Module Son más alargados, de 13 cm, con

múltiples configuraciones en cuanto al número de contactos, entre las

cuales se encuentran 168, 184, 214 y 240 contactos, que se distribuyen

uniformemente en la parte inferior del módulo, a ambos lados del circuito

impreso. Son de 64 bits y 128 bits, por lo que se montan

independientemente en los zócalos de la placa madre, salvo que la

placa madre disponga de un bus de doble canal, en cuyo caso se

montarían por parejas de módulos idénticos. Se fabrican módulos para

voltaje estándar (5 voltios) o reducido desde 3.3 hasta 1,8voltios, por lo

que debemos tener muy claro este dato antes de sustituir o incluir un

módulo nuevo en una placa madre. Los zócalos utilizados para estos

módulos son generalmente negros.

Ilustración 3.12. Módulos SIMM de 184 y 240 contactos.

Los módulos de memoria tienen la ventaja de que son extraíbles y

fácilmente intercambiables, permitiendo las actualizaciones y ampliaciones

necesarias en los sistemas. Generalmente tienen algún sistema de guía y

enclavamiento mecánico que asegura la correcta posición de los contactos

eléctricos, así como la fijación adecuada quedando inmovilizados y evitando de

esta forma que se salgan fácilmente de su posición.

3.4 Memorias caché.

La memoria caché es una memoria ultra rápida de pequeño tamaño que se

sitúa entre la memoria RAM del sistema y el microprocesador, de forma que en

ella se almacenan los datos o código de programa que va a utilizar el

microprocesador en cada momento. Un circuito electrónico con un algoritmo

muy complicado denominado controlador caché es el encargado de intuir en

cada momento los datos que con más probabilidad utilizará el microprocesador,

extrayéndolos de la memoria RAM del sistema y llevándolos a la memoria

caché antes de que el procesador los requiera. Cuando los datos de la caché

quedan obsoletos, el controlador caché debe retirarlos para dejar espacio a

otros nuevos y así poder repetir el proceso indefinidamente. La memoria caché

se construye con memoria estática, en lugar de dinámica, con tiempos de

acceso inferiores a 1 ns. Si esta memoria se incorpora dentro del

microprocesador podremos hacerla trabajar a la velocidad del núcleo de la

CPU, que funciona mucho más rápido que los buses externos y, por tanto, el

éxito está asegurado.

Para una gestión eficiente de la memoria Caché hace falta un buen

controlador, que sea capaz de intuir en cada momento la información, tanto de

datos como de código, que el procesador va a necesitar. Para ello, los

diseñadores de microprocesadores y placas madre invierten muchos esfuerzos

en el desarrollo de estos circuitos de control que van, por una parte, integrados

en el procesador (caché L1 y L2) y por otra en el chipset de la placa madre (L2

y L3). De la eficiencia de estos controladores depende en gran medida la

eficiencia del sistema. Debemos tener en cuenta que la relación entre el

tamaño de la memoria caché y el aumento de eficiencia del sistema no es lineal

y llega un momento en el que el aumento de memoria caché apenas supone

incremento en la eficiencia del sistema. Por este motivo se recurre a escalar la

memoria caché, creando niveles que se acoplan en cascada de forma que van

aumentando su tamaño según se van separando del núcleo de la CPU. Así

podremos hablar de los siguientes tipos de memoria Caché.

Caché L1. Se denomina así a la memoria caché que se integra en el

microprocesador, por lo que su velocidad es la misma que la del núcleo del

procesador y su amplitud de datos puede ser de 64 y 128 bits. La dimensión de

esta memoria es muy reducida y oscila entre los 16KB y 64KB (mitad código y

mitad datos), salvo en los microprocesadores utilizados en equipos servidores

que utilizan hasta 1 o 2 MB de caché L1.

Caché L2. Esta caché en principio esta fuera del microprocesador,

aunque son muchos los modelos de procesadores que también la incluyen en

su interior o en la misma placa donde va montado el microprocesador (Slot 1 y

Slot A), formando un bus de alta velocidad, entre la placa y el micro. A esta

arquitectura se la denomina Bus Dual Independiente (Dual Independent Bus) y

consiste en un bus caché L2 de alta velocidad más un bus del sistema con

anticipación que hace posible múltiples transacciones simultáneas. En los

procesadores y placas madre actuales, el tamaño de la memoria caché L2

viene a ser de 256 MB a 2 MB.

Ilustración 3.13. Módulos de memoria caché montados en lplaca madre.

La caché de nivel 1 no es ampliable, puesto que se encuentra en el

interior del chip del procesador, pero la caché de nivel 2, en muchas placas

madre sí lo es y se realiza por medio de chips que se insertan en los

correspondientes zócalos de la placa base (placas antiguas), o en módulos de

ampliación similares a los SIMM que se insertan en una ranura o slot de la

placa madre destinado a tal efecto.

Ilustración 3.14. Detalle de un módulo de memoria caché insertado en su slot correspondiente

Caché L3. Como se comentó anteriormente, algunos microprocesadores como

el Intel Xeon integran la caché L2 en su interior, por lo que la caché que se

incluye en la placa madre pasa a denominarse caché L3. En este caso, el

tamaño de la memoria caché L3 alcanza hasta los 4 MB.

No hay comentarios:

Publicar un comentario